So you have a schematic. How do

you lay out your custom board? In this article, we'll go over the

challenges and solutions I came across in designing a custom PCB for an

inclinometer subsystem.

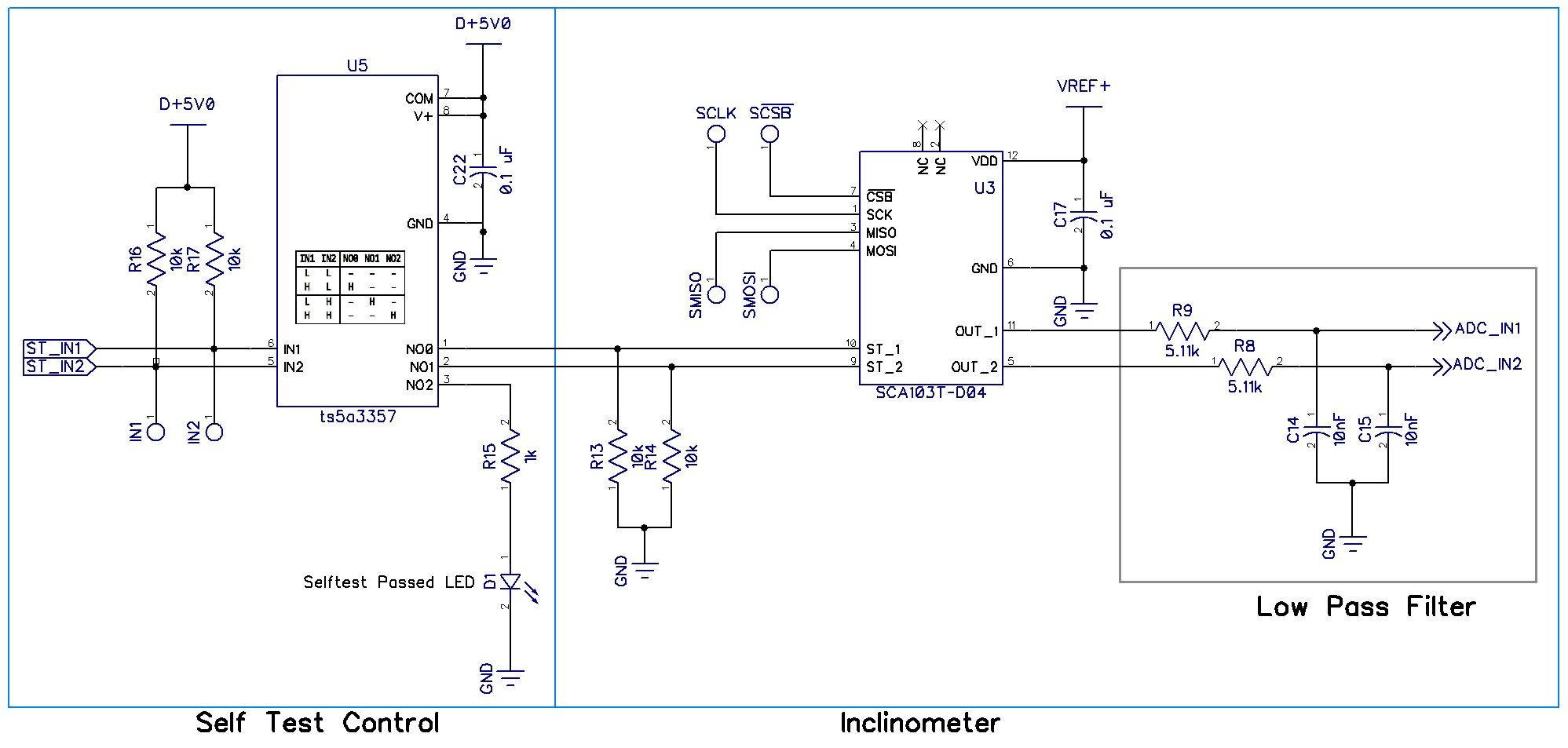

This article is part of a series explaining the process of designing an inclinometer subsystem around a muRata SCA103T-D04 inclinometer IC. You can check out the full project below:In the previous article, I went over the details of how I created my schematic design for the inclinometer subsystem. In this article, we'll discuss the next step in the process: board layout.

The final board we're laying out in this article

No two designers will create identical layouts and few designers will layout the same schematic in the exact same way twice.

There are multiple competing considerations in every PCB design, and sometimes small errors are allowed to persist simply because it would take too long to fix the cascade of changes that occur after moving a part, a via, or a trace. To quote the poet Paul Valery, “A work is never completed except by some accident such as weariness, satisfaction, the need to deliver, or death.”

With that in mind, let's take a look at how we went from schematics like these:

To a PCB design like this:

Isolating the Voltage Reference IC

Let's start with the voltage reference IC, the LT1027LS8. As we discussed in the previous article, this IC requires that three or preferably four slots be used to thermally and mechanically isolate its section of the PCB from the rest of the board.Thermal isolation of the voltage reference is important to mitigate the Seebeck effect or thermocouple effect. Anytime two dissimilar metals (or semiconductors) have their contact point heated, a potential difference is established across the junction. The voltage may be small, but for sensitive devices (such as a voltage reference), it can be enough to disturb the circuit.

So how do we address this issue in our design?

The solution is to generate less heat around the sensitive area of the circuit board and, in this case, the slots cut into the PCB limit the amount of thermal energy that can migrate from other parts of the board. Additionally, the removal of the power and ground planes directly underneath the device will help to prevent heat from flowing to the device from the narrow areas of the board that connect to the rest of the PCB.

The LT1027LS8 datasheet (linked above) also optionally recommends a polyester capacitor to reduce noise. I chose to extend the capacitor over one of the slots cut into the board to keep the protected cut-out area as small as possible. Electrically this approach is fine; mechanically, this might create a point of stress, but I did not perform a finite element analysis (FEA) to determine how much.

Another solution recommended by the datasheet is a guard ring, used to maintain output precision.

What Is a Guard Ring?

Solder

mask, also known as solder resist, is put on a printed circuit board

towards the end of the board manufacturing process. It helps prevent

oxidation of copper and discourages solder bridges between closely

spaced pads during board assembly. Solder resist is a very good

insulator; however, if a potential difference exists between adjacent

bits of copper, it still allows some small amount of current to flow (in

the picoamp range). In some cases, these leakage currents need to be

minimized if extremely high precision is required.

The

generally accepted solution is to include a guard ring. A guard ring is

maintained at approximately the same electrical potential as the parts

of copper that you are trying to protect.

You can see the guard ring I used for this design in the image below.

The guard ring portion of the PCB

In our case, the NR (noise reduction) pin of the voltage reference is maintained at 4.4V, so a resistive divider (R11, R12) is used to generate that same voltage. The resistive divider is attached to a trace that surrounds the NR node.

Since the guard ring is at the same potential as the NR node, there will be no current flow into or out of the NR pin. Removing solder resist around the guard ring further prevents leaking of current from the guard ring into the surrounding copper. To prevent copper oxidation, the traces should be covered with small amounts of solder.

R10

(not shown in the image above) is a small 10 kΩ trimming potentiometer

used to make small changes to the output voltage. C18 and C19 are decoupling capacitors.

Protecting the Signal Path

I routed the inclinometer’s two analog output signals such that they have identical trace lengths, used rounded corners, and surrounded the traces with via stitching. These features are not necessary, but they were easy to incorporate and would be worthwhile if they provide even a small improvement in signal quality.

A look at the signal traces

The signal traces encounter R8 and R9, 5.11 kΩ 0.1% resistors that form part of the first low-pass filter. The package size of those resistors is just large enough to allow a guard trace to pass between the pads. The guard trace, which is connected to the output of the buffer, reduces the (already very low) leakage current through the solder mask. This is complete overkill for this board, but guard rings are free and I was trying to do everything I could to maximize the precision of the inclinometer measurements.

Only two channels of the buffer are used, so the other two output channels are floated per datasheet recommendation and the input channels are tied to 2.5V. Tying the outputs to 2.5V was a matter of routing convenience more than anything else, although having the inputs at a voltage near the middle of the 0 to 5 V supply range certainly will not hurt anything.

From there, the sensor signal encounters a second low-pass filter composed of R3, R4, C6, C7, and C8; this filter is recommended by the datasheet for the AD8244.

The second low-pass filter (R3, R4, C6, C7, and C8) is shown at the top of the image.

After passing through the filter, the signals finally arrive at the successive approximation register ADC,

which digitizes the signals and passes the resulting data through SPI

to the MSP430. In a larger PCB, the MSP430 might be placed next to the

ADC, followed by the CP2102N. However, the MSP430 and the CP2102N can

generate heat and, in this design, they are placed at opposite edges of

the board.

Board Layer Considerations

As I mentioned in the full project article, this board has

four layers: two exterior layers for components and signals, one layer

for ground, and one layer for mixed power.

Top Layer

The

top layer of this board holds many analog and digital signal lines, as

well as a large copper pour tied to the multiple-layer ground net with

an assortment of vias.

The top layer of the PCB

Second Layer

The

second layer of the PCB has the 9–12VDC input net (red), the ground net

(dark green), the 2.5VDC net (light green), and the 3.3V net (orange).

This layer demonstrates several decisions that affect the quality of

design.

Beginning

with the 9-12VDC input net (red), you will see that an exclusion keeps

the net from filling the area between the four mechanical cut-outs. This

is done to satisfy the datasheet recommendation for the voltage

reference. Removing the copper reduces the amount of noise that is

coupled into the voltage-reference circuitry, and it also discourages

the transfer of heat generated by other components.

The

ground-net polygon (dark green) was added to this layer of the board to

prevent noise from the 3.3V net from coupling to the signal lines. This

ensures that the signals on the top layer have the lowest noise

possible.

Finally, the 3.3V net (orange). You’ll notice a large

hatched fill on the left-hand side. This exists to lower the capacitive

coupling between the 3.3V copper pour and the MSP430 capacitive-touch

lines. An additional small hatched fill is on the right side of the

board for the USB traces.

Third Layer

The

third layer of the PCB is one large ground pour. Hatched fills are

again present for the MSP430 capacitive touch lines and the USB data

lines, but otherwise this layer is rather unremarkable.

Fourth Layer

This

layer houses the MSP430, the CP2102N, and the LDOs. These are the parts

of the circuit most likely to generate heat. They were placed on the

bottom of the board so that, if needed, they could be connected to

protrusions on the aluminum carrier with thermal paste for heat

dissipation. I designed the carrier as a means of securely mounting the

inclinometer board.

In closing, I wouldn’t consider this PCB design to be optimal. However, it is a functional design and incorporates interesting layout techniques that you might find useful to consider for future projects.

The next article will discuss several aspects of this project's source code.

Please leave any comments or questions below!

No comments:

Post a Comment