The instruction set architecture

(ISA) is truly a place where software and hardware meet: it’s an

abstraction that describes how a processor can be programmed to perform

certain actions, using machine code. This article explores some of the

history behind how ISAs were developed.

At the lowest level,

instructions are provided in binary, describing everything from

addressing modes, registers, memory layout, interrupt and exception

handling, I/O, and of course, instructions for the processor (ADD, SUB,

etc).ISAs come in several different flavors. Many are proprietary (think AMD), while others are paving the way for open source (think RISC-V). To help get a feel for what’s out there, here’s a brief primer on the history, evolution, and characteristics of a select few ISAs, starting with those developed by Digital Equipment Corporation (DEC).

DEC was a computer systems vendor that operated from 1957 until its eventual acquisition by Compaq in 1998. The company was best known for its minicomputers, the PDP and the VAX, and was one of the most successful tech companies of the time. Part of DEC's legacy is in its ISAs, such as VAX, Prism, and Alpha.

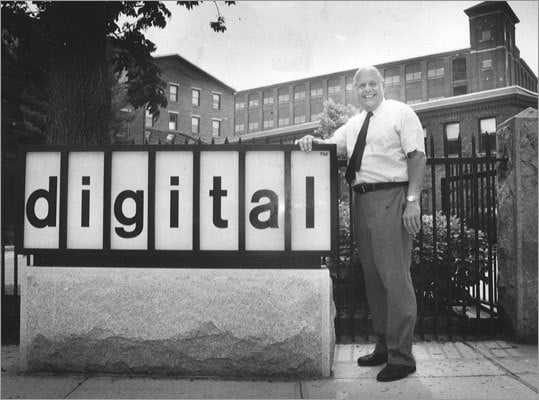

DEC founder, Ken Olsen, in front of the company headquarters that was founded inside an old mill. Image courtesy of Boston.com.

VAX (1977)

VAX, which stands for “Virtual Address eXtension”, was developed by DEC in the 70s for their VAX minicomputers. It first appeared in the VAX-11/780 in 1977.VAX was a 32-bit Complex-Instruction-Set-Computer (CISC) ISA designed for DEC’s VMS operating system. CISC was a way of abstracting assembly language programming into a more intuitive set of instructions. The VAX ISA is cited as being the birth of CISC by some computer historians. The VAX ISA challenged the idea that high-level compilers could not produce the same quality of assembly language programming done by an actual person.

The VAX-11/780 computer. Image courtesy of the Computer History Museum.

The success of the VAX ISA is probably most evident in the fact that the performance of VAX-11/780 became a benchmark for CPU performance—the term “VAX Unit of Performance” (VUP) was coined, and so a system 10 VUPS would be 10 times faster than a VAX machine.

Some features of VAX include:

- Virtual addressing

- Orthogonal Instruction Set (any instruction can be used in any addressing mode)

- Register masks

- 16 general purpose registers

- An expansive selection of addressing modes including: literal, immediate, load effective, register/register deferred, postincrement/predecrement, displacement/displacement deferred, indexed, and several combinations of the above

- Instructions such as ADD, COMPARE, IN, JUMP IF, etc

Prism (1988)

Prism was a research project that DEC began in 1982. By this time, the Reduced-Instruction-Set-Computer (RISC) ISA was becoming a new, competing standard, and so work into a high performance, competitive 32-bit RISC ISA became a new goal of the company. Prior to Prism, DEC had four other projects for RISC ISA development: SAFE, Titan, Cascade, and HR32. Of the four, only SAFE proposed a 64-bit ISA.Prism’s original design was for a 64-bit system, but ultimately designers chose 32-bits, with extensions for vector instructions and 64-bit registers. A feature called epicode (extended processor instruction code) which also exposed further special instructions.

Two derivatives of Prism would also be developed, including MicroPrism for CMOS based microprocessors, and Crystal for ECL based systems.

In 1988, Prism was canceled due to internal disagreements on the focus and direction of DEC against increasingly competitive business adversaries. The in-house developed ISA was abandoned for off-the-shelf options in order to try to stay competitive in the workstation market.

Alpha (1992)

The Alpha ISA, also know as DEC Alpha or Alpha APX, was first introduced in 1992 and used until 2007.Alpha is a 64-bit, RISC-based ISA that is based off of the 32-bit Prism ISA project. The changes made in Alpha, compared to Prism, largely centered around the ability to support the VMS operating system, and the fact that many RISC-based ISAs were now being implemented in 64-bit. It also had to be backward compatible with the VAX ISA used in previous DEC microprocessors.

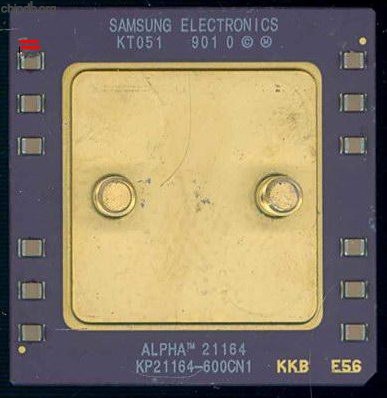

Alpha was developed for high performance systems, and the microprocessors it was implemented in broke many firsts: the Alpha 21064 CMOS based microprocessor had an operating frequency that was competitive against ECL based mainframes; Alpha 21164 was the first microprocessor to have a secondary cache on chip; and Alpha 21364 had the first on-chip memory controller.

The Alpha 21164 chip, manufactured by Samsung. Image courtesy of ChipdB.

Alpha was discontinued after a series of events saw DEC being sold to Compaq in 1998. Compaq was using Intel chips, sold the Alpha IP to Intel where it was discontinued. The last Alpha-based systems continued to be sold by Hewlett-Packard, which bought Compaq, until 2007.

Features of Alpha include:

- 32 integer registers (R0-R31), 32 floating point registers (F0-F31), floating point control register (FPCR), 2 lock registers (LR0-LR1), and a program counter

- Data types: quadword (64-bit), longword (32-bit), IEEE T-floating-point (64-bit, double precision), IEEE S-floating-point (32-bit, single precision), VAX G-floating-point (64-bit, double precision), VAC F-floating point (32-bit, single precision)

- Six 32-bit instruction formats

- Logic, arithmetic, and control instructions

- Four extensions: Byte-Word Extension (BWX), Motion Video Instruction (MVI), Floating-Point Extension (FIX), and Count Extension (CIX)

- To maintain high-speed performance features like branch delay, suppressed instructions, and byte load/store instructions were eliminated

We'll be covering the history of other ISAs in the future. What would you like to know when it comes to ISAs? Share your thoughts in the comments below.

No comments:

Post a Comment