In addition to data centers, the

new 3D System In Package (SiP) FPGAs are targeted for data-centric

embedded and network applications.

The challenges presented by the diffusion of Artificial Intelligence

AI-based functions are now present not only at the network level but also up at the cloud and down at the edge, where the electronic system meets the world it measures or controls. And, everywhere, rapidly changing and evolving standards require local hardware-based solutions to meet these challenges.As noted by Intel’s Dan McNamara, “The race to solve data-centric problems requires agile and flexible solutions which can move, store and process data efficiently. Intel Agilex FPGAs deliver customized connectivity and acceleration while delivering much-needed improvements in performance and power for diverse workloads.”

To meet those challenges, the new family of solutions boasts up to a 40% improvement in maximum clock speed (Fmax) when compared to the company’s Stratex 10 FPGAs.

Image source: Intel

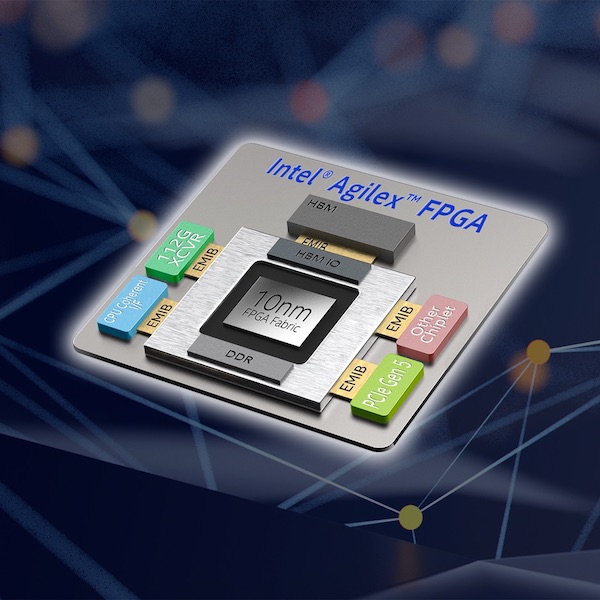

Intel's new Agilix family combines FPGA fabric built on Intel’s 10nm process with heterogeneous 3D system-in-package (SiP) technology. This allows the integration of analog, memory, custom computing, custom I/O, and application specific IC (ASIC) device tiles into a single package along with the FPGA fabric.

Having it all in one package saves board space, reduces the BOM and increases overall system reliability.

New Features Available with Agilex

- Compute Express Link (CXL), a low latency interconnect between the CPU and workload accelerators, such as GPUs, FPGAs and networking.

- Improvement in speed and/or a decrease in required power when compared to Intel’s established Stratix 10 FPGAs.

- Unique among FPGAs, it supports hardened BFLOAT16 (which is based on a 16-bit, floating point architecture) and up to 40 TFLOPs of DSP Performance (FP16 Configuration).

- Transciever Data Rates of up to 112 Gbps supported.

- Memory support for DDR5, HBM, Intel Optane.

- Peripheral component interconnect express (PCIe) Gen 5 for higher system bandwidth.

A look inside Intel’s Agilex FPGA. Image courtesy Intel.

What the Competition has to Offer

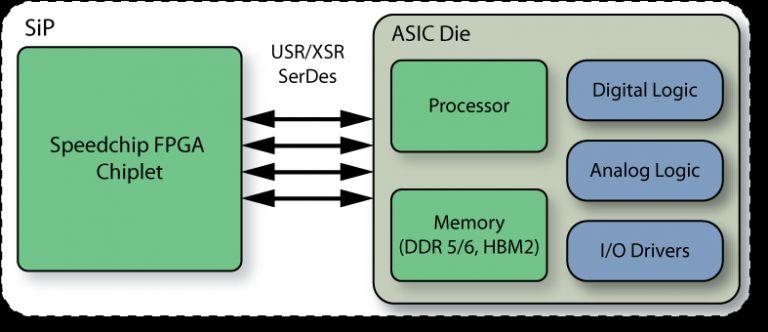

SiPs offer a great advantage over Systems on a Chip (SoC), and that is the opportunity to, in essence, mix and match. Existing components that serve a design’s purpose can be mated with the most advanced FPGA, to save money and get the SiP into production sooner.This basic nature of the SiP contributes to its flexibility and makes it difficult to compare apples to apples. As such, there is even more diversity of features and specializations here than in many other categories of electronic components. Here are two examples.

- Achronix Semiconductor incorporates its Speedchip “Chiplet” FPGAs into a SiPpackage along with an ASIC die.

Image courtesy Achronix.

The Achronix units are targeted at applications such as encryption, decryption and compression, packet processing, traffic management and 5G physical layer signal processing.

- Mercury Systems BuiltSECURE SIPs are FPGA-based packages aimed largely aimed at military applications. They are built in defense microelectronic activity (DEMA) accredited facilities. Additionally, they work over a temperature range from -55°C to +125°C.

What do you think of the way new components are addressing the needs of big data? Let us know in the comments.

No comments:

Post a Comment