Learn about I2C and

some of the design challenges that comes with it, including logic

thresholds, factors that affect capacitance, and minimum and maximum

pull-up resistance.

About I2C

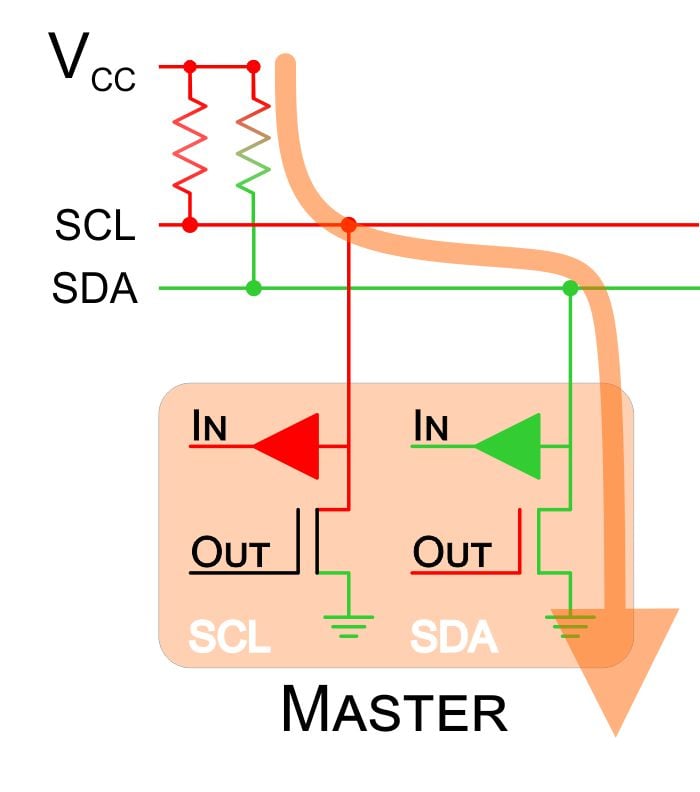

I²C is a multi-master, multi-slave serial interface that allows microchips to communicate with one another at standard speeds of 100 kHz (Standard Mode), 400 kHz (Fast Mode), 1 MHz (Fast Mode Plus), and 3.4 MHz (High-Speed Mode).One of our previous articles, I²C Bus Hardware Implementation Details, explains the mechanism in great detail. The bus specification can be found on NXP's website.

Shown above is an I²C hardware configuration along with simplified clock and data waveforms.

Real-life I²C transactions are not the square-wave pulses commonly depicted in drawings. The circuits have an inherent impedance due to the presence of parasitic capacitance and the use of pull-up resistors.

Logic-high to logic-low transitions involve current discharging through the low-impedance channel of an NMOS transistor—these transitions are rapid. The logic-low to logic-high transitions, however, involve current that must flow through a relatively high-value pull-up resistor. Lower pull-up resistance leads to faster transitions but also to higher current consumption (when the signal is logic low); higher pull-up resistance leads to slower transitions and reduced current consumption. The value of the resistor chosen becomes increasingly important at higher frequencies.

Positive transitions appear rounded due to the pull-up resistors in the logic-low-to-logic-high current path.

Any increase in bus capacitance or resistance will increase the logic-high transition time. At a certain point, the potential difference will not even reach the logic-high threshold, or it will not remain there long enough before transitioning back to logic low.

In the above graph, the RC time constant is too large and the logic-high threshold is not reached.

Different I²C devices can have different logic thresholds. The preceding graphs all assume transitions with

and , but this is not always the case. The ADP5062, for example, has transitions at and

.

Chips with different threshold voltages can be used on the same bus; when this is the case, calculations should be made using the highest logic-high threshold voltage and lowest logic-low threshold voltage.

This graph shows a hypothetical logic-low threshold voltage of 0.7 V and a hypothetical logic-high threshold voltage of 1.3 V. These low values increase the time spent in the logic-high state without significantly altering the time spent in the logic-low state. This configuration allows for higher-frequency operation.

Capacitance

The NXP specification states that the maximum overall bus capacitance is 400 pF for Standard Mode and Fast Mode devices and 550 pF for Fast Mode Plus devices. You should not add capacitors to the I²C lines in order to reach these upper capacitance limits—a lower bus capacitance is better.Dielectrics

Your circuit board base material can affect the overall capacitance of your bus. The dielectric constant for most PCB base materials is in the range of 2.5≲ε≲5 (ε is frequency dependent).

This graph shows the effect of dielectric constant on the capacitance of a microstrip line.

Sources of Increased Bus Capacitance

Sources of bus capacitance include the ICs on the bus, microstrip traces, and nearby signal traces and power planes. Also, capacitive fringe effects cannot be ignored in the case of small circuit boards or when I²C traces are near the edge of the board.Any metal or dielectric near the I²C lines can increase your overall capacitance, but in many cases the effect is negligible.

Insignificant Sources of Capacitance

Parasitic bond and package capacitance is not something that you can control. Fortunately, it’s only approximately 1-2 pF per signal line (see this document for more information). In other words, it’s not going to be a significant consideration in your overall circuit. This 1-2 pF capacitance is included in the estimate in the following paragraph.Significant Sources of Capacitance

ICs Used in the Circuit

The NXP specification lists a “maximum capacitance for each I/O pin” of 10 pF. Each IC that you add will increase the overall bus capacitance by approximately 10 pF (see the datasheet for the specific IC), and then you must also consider the capacitance associated with the traces that connect the IC to the bus.Copper Trace Capacitance

When we say "copper trace capacitance" here, we're referring to single trace over dielectric over ground. The capacitive coupling between the I2C signal lines and the ground plane can be significant if the ICs are far from each other, or multiple ICs are on the I2C bus. For long runs, separate the I2C lines from one another by several trace widths (or place the Vdd and ground traces between the signal traces) to reduce capacitive coupling effects between the two signal lines.

To calculate the capacitive coupling between a signal and a ground plane (or a power plane), use the following equation, which takes into account fringe effects.

Modified from "High Speed Digital Design" by Johnson and Graham

The calculation below is an example calculation for adjacent layers of a four-layer stack with the following realistic parameters: εFR4 = 4.5, trace width = 0.13 mm, layer height = 0.23 mm, trace thickness = 0.035 mm.

Effect of Apertures on Microstrip Capacitance

It is possible to decrease the capacitance by increasing the distance to the ground plane—this is accomplished by placing the signal traces on layers that are one or more layers removed from the ground plane. It is also possible to remove copper from a plane layer so as to create a copper void underneath the trace. This void is referred to as an aperture.

Resistors

As an example, let’s say that we have a 3.3 V bus and want to limit the current to 3 mA.

Low-valued pull-up resistors produce faster transitions and a “sharper” wave, but they also lead to higher power dissipation.

Calculating the Maximum Value of Pull-Up Resistors

To ensure proper functionality, the designer must ensure that an I2C device’s timing requirements are satisfied.

The above graph illustrates the segments of an I2C transaction that correspond to rise time, fall time, time spent in logic-low state, and time spent in logic-high state. Appropriate values for these timing parameters are typically indicated in a device’s datasheet. The graph is not to scale.

High-value pull-up resistors will increase the transition time to the logic-high threshold, which might prevent the IC from functioning correctly.

The logic-high rise time is too great, and the logic-high threshold has not been met. Consequently, devices on this bus will not be able to communicate.

Calculating the maximum value of a pull-up resistor requires knowing the rise-time requirement. Then, exponential functions are used to model the curve and find the time required to reach the logic-high threshold voltage after passing the logic-low threshold voltage.

The initial equation arranged to solve for the time to reach the logic-high threshold voltage

The initial equation arranged to solve for the time to reach the logic-low threshold voltage

Rearrange to solve for

and it becomes

Summary

The value of an I²C pull-up resistor must be large enough to reduce unnecessary current consumption and small enough to produce an acceptable rise time. The calculations presented in this article can help you to find a suitable value, but if you really want to optimize your I²C bus, you will probably need to measure the signals with an oscilloscope (use a low-capacitance probe if possible) and adjust the pull-up resistance until you achieve the desired timing characteristics.

No comments:

Post a Comment