The most powerful and important features are interrupts in 8051 microcontroller.

In most of the real-time processes, to handle certain conditions

properly, the actual task must be halt for some time – it takes required

action – and then must return to the main task. For executing such type

of programs, interrupts are necessary. It entirely differs from the

polling method wherein the processor must check sequentially each device

and ask whether the service is required or not while consuming more

processor time.

Interrupts in 8051 microcontroller are

more desirable to reduce the regular status checking of the interfaced

devices or inbuilt devices. Interrupt is an event that temporarily

suspends the main program, passes the control to a special code section,

executes the event-related function and resumes the main program flow

where it had left off.

Interrupts are of different types like

software and hardware, maskable and non-maskable, fixed and vector

interrupts, and so on. Interrupt Service Routine (ISR) comes into the

picture when interrupt occurs, and then tells the processor to take

appropriate action for the interrupt, and after ISR execution, the

controller jumps into the main program.

Types of Interrupts in 8051 Microcontroller

The 8051 microcontroller can recognize

five different events that cause the main program to interrupt from the

normal execution. These five sources of interrupts in 8051are:

- Timer 0 overflow interrupt- TF0

- Timer 1 overflow interrupt- TF1

- External hardware interrupt- INT0

- External hardware interrupt- INT1

- Serial communication interrupt- RI/TI

The Timer and Serial interrupts are

internally generated by the microcontroller, whereas the external

interrupts are generated by additional interfacing devices

or switches that are externally connected to the microcontroller. These

external interrupts can be edge triggered or level triggered. When an

interrupt occurs, the microcontroller executes the interrupt service

routine so that memory location corresponds to the interrupt that

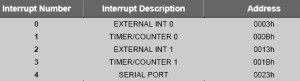

enables it. The Interrupt corresponding to the memory location is given

in the interrupt vector table below.

Interrupt Structure of 8051 Microcontroller

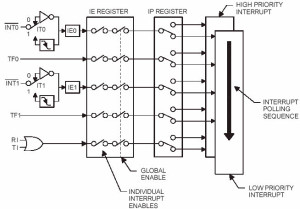

Upon ‘RESET’ all the interrupts get

disabled, and therefore, all these interrupts must be enabled by a

software. In all these five interrupts, if anyone or all are activated,

this sets the corresponding interrupt flags as shown in the figure. All

these interrupts can be set or cleared by bit in some special function

register that is Interrupt Enabled (IE), and this in turn depends on the

priority, which is executed by IP interrupt priority register.

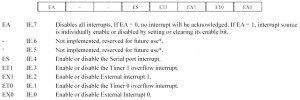

Interrupt Enable (IE) Register:

This register is responsible for enabling and disabling the interrupt.

It is a bit addressable register in which EA must be set to one for

enabling interrupts. The corresponding bit in this register enables

particular interrupt like timer, external and serial inputs. In the

below IE register, bit corresponding to 1 activates the interrupt and 0

disables the interrupt.

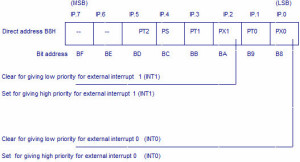

Interrupt Priority Register (IP):

It is also possible to change the priority levels of the interrupts by

setting or clearing the corresponding bit in the Interrupt priority (IP)

register as shown in the figure. This allows the low priority interrupt

to interrupt the high-priority interrupt, but prohibits the

interruption by another low-priority interrupt. Similarly, the

high-priority interrupt cannot be interrupted. If these interrupt

priorities are not programmed, the microcontroller executes in

predefined manner and its order is INT0, TF0, INT1, TF1, and SI.

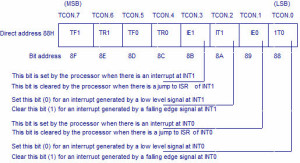

TCON Register: In

addition to the above two registers, the TCON register specifies the

type of external interrupt to the 8051 microcontroller, as shown in the

figure. The two external interrupts, whether edge or level triggered,

specify by this register by a set, or cleared by appropriate bits in it.

And, it is also a bit addressable register.

Interrupt Programming in 8051

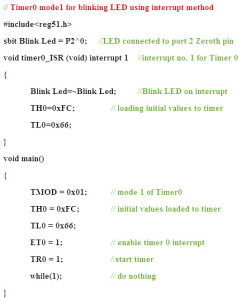

1.Timer Interrupt Programming

Timer 0 and Timer 1 interrupts are generated by the timer register bits TF0 and TF1. These interrupts programming by C code involves:

- Selecting the timer by configuring TMOD register and its mode of operation.

- Choosing and loading the initial values of TLx and THx for appropriate modes.

- Enabling the IE registers and corresponding timer bit in it.

- Setting the timer run bit to start the timer.

- Writing the subroutine for the timer for time required and clear timer value TRx at the end of subroutine.

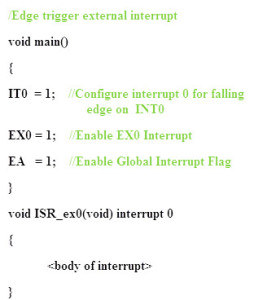

2.External Hardware Interrupt Programming

8051 microcontrollers consists of two

external hardware interrupts: INT0 and INT1 as discussed earlier. These

are enabled at pin 3.2 and pin 3.3. These can be edge triggered or level

triggered. In level triggering, the low at pin 3.2 enables the

interrupt, while at pin 3.2 – the high to low transition enables the

edge triggered interrupt. This edge triggering or level triggering is

decided by the TCON register that has been discussed above. The programming procedure in 8051 is as follows:

- Enable the corresponding bit of external interrupt in IE register.

- If it is level triggering, just write the subroutine appropriate to this interrupt, or else enable the TCON register bit corresponding to the edge triggered interrupt – whether it is INT0 or INT1.

3.Serial Communication Interrupt Programming

Serial communication interrupts come

into picture when there is a need to send or receive data. Since one

interrupt bit is set for both TI (Transfer Interrupt) and RI (Receiver

Interrupt) flags, Interrupt Service routine must examine these flags to

know the actual interrupt.

The logical OR operation of these two

flags (RI ands TI) causes this interrupt, and it is cleared by the

software alone. Here, a special register SCON is used for controlling communication operation by enabling the corresponding bits in it.

- Configure the IE register for enabling serial interrupt

- Configure the SCON register for receiving or transferring operation

- Write subroutine for this interrupt with appropriate function and clear TI or RI flags with in this routine.

This is all about interrupts in 8051

microcontroller, types, their structure and programming. Hope you might

have received good information from this article. Also, you can write to

us in the below comment section for the real-time implementation of microcontroller projects so that we can assist you for a better hands-on experience.

No comments:

Post a Comment